Четырёхкратная скорость передачи данных

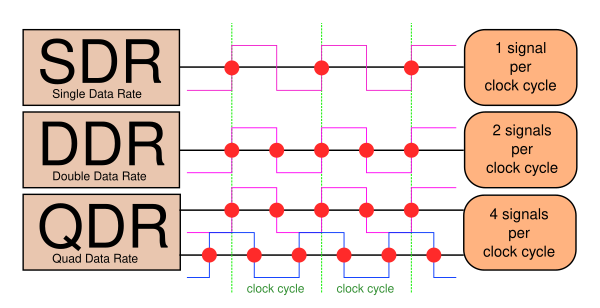

Четырёхкра́тная ско́рость переда́чи да́нных (англ. Quad data rate QDR) — стандарт оперативной памяти, при котором данные передаются в четырёх точках тактового цикла: на фронтах и спадах тактового сигнала, а также в двух промежуточных точках между ними. Промежуточные точки определяются вторым тактовым сигналом, сдвинутым по фазе на 90° относительно первого. В результате за один тактовый цикл по каждой линии сигнала передаются четыре бита данных[1].

В системе с четырёхкратной скоростью передачи данных линии передачи данных работают на частоте, вдвое превышающей частоту тактового сигнала. Это отличается от систем с двойной скоростью передачи данных, в которых линии передачи данных и тактового сигнала работают на одной частоте[1].

Технология четырёхкратной скорости передачи данных QDR была представлена компанией Intel в процессоре Pentium 4 с ядром Willamette и впоследствии использовалась в процессорах серий Atom, Pentium 4, Celeron, Pentium D и Core 2. Эта технология позволила Intel производить чипсеты и процессоры, способные обмениваться данными на скоростях, характерных для традиционной технологии фронтальной шины (FSB) с диапазоном от 400 MT/с до 1600 MT/с, при этом поддерживая более низкую и, следовательно, более стабильную фактическую тактовую частоту от 100 МГц до 400 МГц[2].

Обзор технологии

Четырёхкратная скорость передачи данных QDR является продолжением развития памяти типа SRAM — статической памяти, которая используется, например, в кэш-памяти современных компьютеров и не требует постоянного обновления содержимого, в отличие от динамической памяти SDRAM. Статическая память обладает большей скоростью доступа к данным, но более дорога в сравнении с SDRAM.

Технология QDR SRAM была инициирована технологическим консорциумом, в состав которого входят компании IDT, Micron, Samsung, Cypress, NEC и Hitachi. Были разработаны спецификации стандартов QDR-I и QDR-II. Технология QDR является родственной по отношению к стандарту двойной скорости передачи данных DDR (Double Data Rate).

Уникальность архитектуры заключается в том, что QDR использует два независимых порта для ввода и вывода, функционирующих на удвоенной частоте (DDR), причём порты могут работать на разных частотах. При такой организации ввода-вывода за один такт передаётся 4 единицы информации, что позволяет увеличить эффективную скорость передачи данных в 4 раза.

Память типа QDR может обладать большой пропускной способностью и низкими задержками, что позволяет ориентировать её на применение в коммуникационных устройствах, функционирующих на частоте свыше 200 МГц.

Конструктивно микросхемы QDR выполняются в виде чипов FBGA размером 13 х 15 мм, что позволяет экономить до 40 % места по сравнению с традиционными чипами BGA размером 14 × 22 мм. Это позволяет выпускать более дешёвые и ёмкие модули, чем для других типов SRAM.

Реальные частоты памяти QDR-I составляют 166 и 200 МГц, для QDR-II — соответственно 250 и 333 МГц. QDR-II обладает бо́льшими задержками и большей плотностью, а также пониженным питанием (1,8 В против 2,5 В у QDR-I). Пропускная способность памяти QDR-II способна достичь 36 Гб/с.

Преимущества архитектуры реализуются главным образом в операциях с частым одновременным чтением/записью данных, предпочтительная форма организации ввода-вывода для такой архитектуры — метод FIFO.

Конструктивно модули плотностью от 9 до 72 Мбит выполняются в виде DIMM с 168 штырьками, а также SODIMM с 144 и 100 штырьками соответственно.

Тип памяти QDR предназначен для использования в телекоммуникационном оборудовании и не ориентирован на использование в персональных компьютерах любого типа[3].

Использование

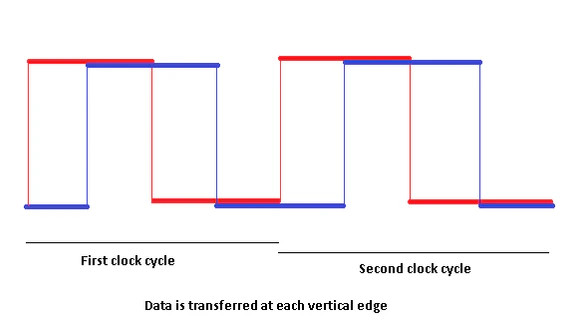

Причины использования четырёхкратной скорости передачи данных QDR вместо двойной скорости передачи данных DDR существенно отличаются от причин перехода с однократной скорости передачи данных SDR на DDR. Переход на DDR позволил производителям памяти передавать данные с частотой, равной частоте тактового сигнала (одна передача данных на каждый переход тактового сигнала), тогда как SDR могла передавать данные только с частотой тактового цикла (одна передача данных на каждый фронт тактового сигнала).

Преимущества технологии четырёхкратной скорости передачи данных QDR проявляются при работе с конфликтами на шине. В современном компьютере может быть несколько процессоров и множество устройств ввода-вывода, которые конкурируют за доступ к памяти. Чтобы справиться с этой конкуренцией, современные системы стремятся обеспечить прохождение сигналов между всеми подключёнными компонентами в пределах одного тактового цикла, при этом устанавливая жёсткое ограничение на максимальную тактовую частоту. Однако после разрешения конфликта передачу данных можно рассматривать как простую однонаправленную точка-точка. В такой простой передаче уже не требуется, чтобы сигналы полностью распространялись в течение цикла; достаточно, чтобы они приходили синхронизировано, управляемые специальным сигналом, называемым «строб». Это сниженное требование к целостности сигнала позволяет осуществлять передачу данных по технологии QDR на скорости, в два раза превышающей тактовую частоту, в отличие от DDR, где скорость передачи данных равна тактовой частоте[4].

В стандарте GDDR5 (5-е поколение памяти DDR SDRAM) часто используется четырёхкратная скорость передачи данных QDR[5].

В суперкомпьютере «Ломоносов» (суперкомпьютер, построенный компанией «Т-Платформы» для МГУ им. М.В. Ломоносова) использовался тип системной сети QDR InfiniBand. Также стандарт QDR использовался в SAGA-220 — суперкомпьютере, созданного Индийской организацией космических исследований (ISRO).

Устройства высокоскоростной памяти, разработанные по спецификации QDR-II SRAM, широко используются для быстрой и эффективной обработки данных. Независимые порты чтения и записи, высокая частота и скорость передачи данных обеспечивают плавную производительность в сетевых, телекоммуникациях и вычислительных приложениях[6][7].