Схема ускоренного переноса

Схе́ма уско́ренного перено́са — комбинационная логическая схема, входит в арифметико-логическое устройство большинства современных ЭВМ микропроцессоров и микроконтроллеров.

Предназначена для параллельного формирования битов переноса при сложении двоичных чисел в сумматоре. Обычно строится каскадным способом, состоит из нескольких схем ускоренного переноса меньшей разрядности, обычно равной натуральной степени числа 2, но существуют и однокаскадные схемы ускоренного переноса, формирующие сигналы переноса для всех битов слова одновременно.

Преимущество этой схемы — существенное ускорение арифметических операций, так как не требуется время для распространения переноса последовательно по всем битам машинного слова, недостаток — повышенная сложность.

Принцип работы

Термины:

Carry Lookahead Unit (CLU) — схема ускоренного переноса.

Carry Look-ahead Adder (CLA) — схема сумматора с ускоренным переносом.

Group propagate (PG) — групповой сигнал распространения переноса.

Group generate (GG) — групповой сигнал генерации переноса.

При использовании схемы ускоренного переноса (LCU) каждый одинарный разряд сумматора вырабатывает сигнал генерации переноса () и сигнал распространения переноса ().

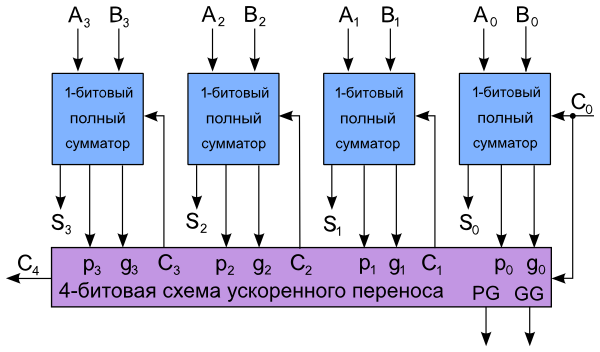

4-битная схема

Одинарные разряды сумматора объединяются в группы по четыре одинарных разряда в каждой группе. Схема ускоренного переноса вырабатывает сигналы переноса групповой сигнал генерации переноса (GG) и групповой сигнал распространения переноса (PG).

Логическое выражение для переноса в одном разряде:

- , где

Здесь точка () означает логическое И (AND), знак сложения (+) - логическое ИЛИ (OR) и символ сложение по модулю 2 ИСКЛЮЧАЮЩЕЕ ИЛИ (XOR)

Для переносов в четырёх разрядах:

Подставив в , затем в , затем в получим окончательные выражения:

Групповой сигнал генерации переноса и групповой сигнал распространения переноса формируются следующим образом:

4-битная схема ускоренного переноса выпускается в интегральном исполнении, например: SN74182 (ТТЛ), MC10179 (ЭСЛ) и MC14582, 564ИП4[1] (выполненная по технологии КМОП).

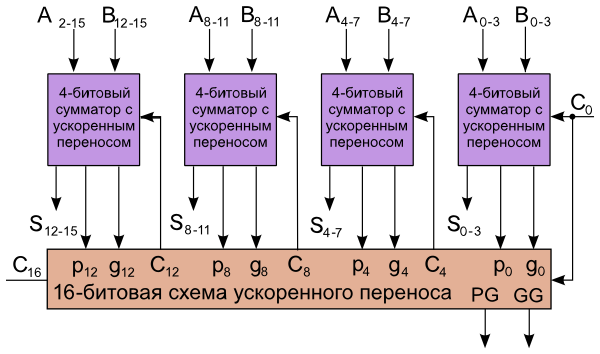

16-битная схема

16-разрядный сумматор может быть создан путём объединения четырёх 4-битных сумматоров с четырьмя схемами ускоренного переноса (4-bit CLA Adder), дополненных пятой схемой ускоренного переноса, которая используется для обработки групповых сигналов генерации переноса — GG и распространения переноса — PG.

Принимаемые на входе сигналы распространения переноса () и генерируемые каждой их четырёх схем сигналы (GG). Затем, схема ускоренного переноса генерирует соответствующие сигналы.

Предположим, что это сигналы PG и это GG из iй, то выходные биты устанавливаются следующим образом:

Подставляя сперва в , затем в , затем в получаем следующее выражение:

соответственно генерирует бит переноса на вход второй схемы; на вход третьей; на вход четвёртой; и генерирует бит переполнения.

Кроме того, можно указать сигналы распространения переноса и генерации переноса для схемы ускоренного переноса:

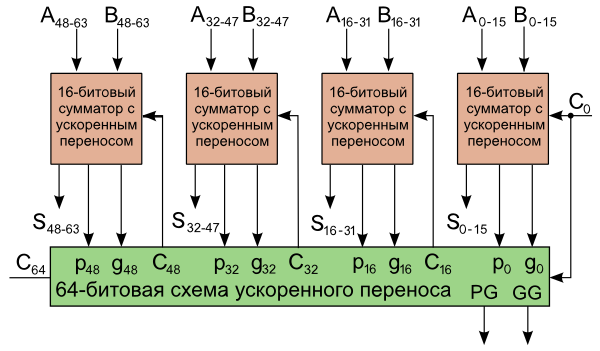

64-битная схема

Объединив четыре схемы сумматора и схему ускоренного переноса вместе, получим 16-битный сумматор. Четыре таких блока могут быть объединены в 64-разрядный сумматор. Дополнительные схемы ускоренного переноса (второго уровня) необходимы, чтобы принимать сигналы распространения переноса () и сигналы генерации переноса() от каждой схемы сумматора.

Достоинства и недостатки

Достоинства:

- Высокая скорость работы.

Недостатки:

- Бо́льшие затраты оборудования

Схемы формирования параллельного переноса имеют существенное преимущество в скорости перед схемами последовательного переноса.

См. также

Литература

- Титце У., Шенк К. Глава 19. Комбинационные логические схемы. 19.5 Сумматоры. 19.5.3. Сумматоры с параллельным переносом // Полупроводниковая схемотехника = Halbleiter-Schaltungstechnik / Пер. с нем. Г. Карабашев. — Додэка XXI, 2008. — 1784 с. — (Схемотехника). — 3000 экз. — ISBN 978-5-94120-200-3, 978-5-94120-201-0, 3-540-42849-6.

Ссылки

Источники

- Воробьев Н. Сумматоры. Определения, классификация, уравнения, структуры и применение. Часть 2

- Сумматоры. Повышение быстродействия параллельных сумматоров. Принцип построения БУП (блок ускоренного переноса).

- Цифровая электроника. Курс лекций. Тема 4. Комбинационные цифровые устройства. 4-3. Сумматоры.

- Сумматор с ускоренным переносом.

- Дискретная математика: Алгоритмы. Многоразрядный сумматор.

- Сумматоры. Комбинационный сумматор с параллельным переносом.